# Bias control Technique for CDMA driver Amplifier to decrease current

Jin-Su Ko, Hyun-Seok Kim, Sung-Gi Yang, Bonkee Kim and Byeong-Ha Park

RF Products Team, Samsung Electronics Co., Ltd.

Suwon P.O. Box 105 Kyunggi-Do, KOREA 440-600

e-mail: liberty859@yahoo.co.kr

**Abstract** — ACPR requirement is constant over wide power range. ACPR at lower output power is excessive in conventional constant bias current. New bias control technique to decrease bias current at lower power level is proposed by implementing hyperbolic tangent function (tanh) with offsets. It is verified indirectly by measurement. The measured bias current is reduced by amount of 22 % over control range compared to the conventional one, in addition to meet ACPR requirement simultaneously over all range of output power.

## I. INTRODUCTION

The circuit blocks used in CDMA RF transmitter require high linearity due to high peak to average ratio. The required linearity of each block is specified with an ACPR (Adjacent Channel Power Ratio) parameter. Minimum standard on the ACPR is specified in IS-95/98 and J-STD-018 such that spurious emission levels shall be less than  $-42$  dBc/30kHz at Cellular and PCS CDMA, respectively, at each condition of offset frequency. In practice, this requirement becomes severe as output power approaches maximum within range of output power. Note that the same amount of ACPR is specified regardless of output power.

Our previous and other works [1], [2] showed that the ACPR is the function of output power ( $P_o$ ) and output intermodulation intercept point (oIP3) and that the relationship of them can be approximated by

$$ACPR = 2(oIP_3 - P_o + \alpha) \quad (1)$$

where the ACPR represents the absolute value and the value of  $\alpha$  is about 10.0 and 6.7 in case of Cellular CDMA when the 3<sup>rd</sup> order and the 5<sup>th</sup> order intermodulation term is considered, respectively. In reality, our experimental results are closer to the simpler 3<sup>rd</sup> order approximation. Eq. (1) means that, in a given condition of constant ACPR, when  $P_o$  is decreased, the oIP3 can be decreased by the same amount.

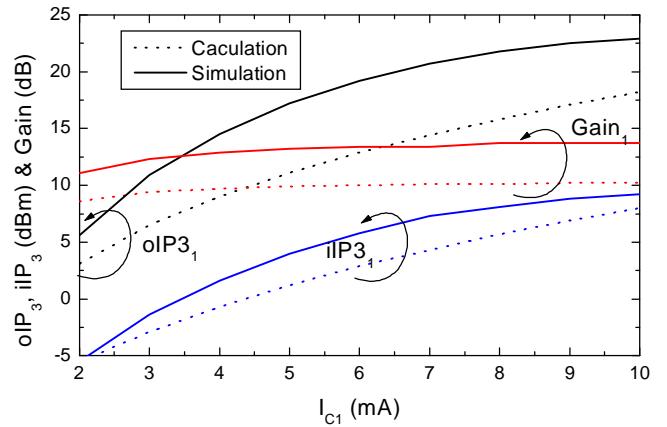

Our previous work [3] shows that oIP3 of cascode amplifier with emitter degeneration inductor is proportional to bias current as shown in Fig. 1. Conventional approach sets bias current high in order to meet high oIP3 at maximum output power. High bias current flows over all range of output power. However, ACPR is excessive over most of range except near maximum output power.

Fig. 1. Typical gain and non-linearity characteristic (iIP3, Gain, and oIP3) vs. collector bias current ( $I_{C1}$ ) in the case of cascode amplifier with emitter degeneration inductor ( $Le1$ ). Here,  $Le1 = 4$  nH, operating frequency = 850 MHz. It is calculation by Volterra series and simulated by HP ads [3]. The iIP3 represents input intermodulation intercept point.

## II. IMPLEMENTATION OF BIAS CONTROL BLOCK

New bias control technique is proposed to decrease bias current within control range of output power. Although bias current is set to low at medium power, the ACPR at medium power can be no worse than one at maximum power because output power becomes low simultaneously.

Usually, gain is proportional to bias current in analog circuit block. However, in the case of RF amplifier using

emitter (source) degeneration inductor as like driver amplifier and LNA, gain does not changed much with various bias current as shown in Fig. 1 and described in [4].

New technique to control bias current monotonically without discontinuity is proposed [5]. The shape of bias current over control voltage is hyperbolic tangent function with offsets such as  $\tanh(\beta(V_{ctrl}-V_{ref})/2)$ . When output power becomes low, bias current decreases to reduce DC power consumption. When high linearity is required at higher power, bias current increases. To reduce bias current furthermore, bias current is fixed to constant as output power goes into maximum power. Then, it is operated on class AB mode due to self-bias.

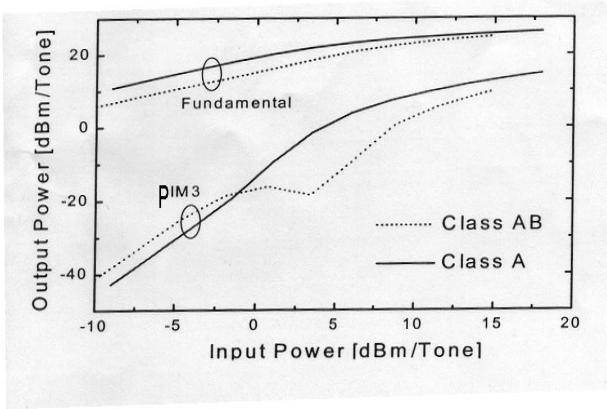

Contrary to anticipation, class AB operation is more linear than class A operation at high output power [1], [6]. As output power goes into near saturation, the third order intermodulation distortion (IMD) output ( $P_{IM3}$ ) of class AB is smaller than that of class A. Typical result of  $P_{IM3}$  and  $P_o$  in class A and AB amplifier is shown in Fig. 2 [1], [6].

Fig. 2. Typical power transfer characteristic on two-tone test in class A and AB amplifier. Due to the indent in  $P_{IM3}$  curve of class AB amplifier, class AB has larger intermodulation rejection at high power region [1], [6].

In the opposite case, that is, when output power is below certain power level, bias current is fixed to constant to prevent the increase of output noise power and to stabilize gain. When bias current is too small, output noise is abruptly increased due to small transconductance and the gain is changed by input power due to self bias by saturated swing. As described in the above, new bias control technique makes bias current constant at both extreme control range and high dynamic range can be obtained.

Recently, such method to set bias current at constant minimum and maximum is suggested in commercial

product [7]. However, it is used to control gain slope and to protect over-current. Within real application range, it is operated on exponential trend rather than our tanh one.

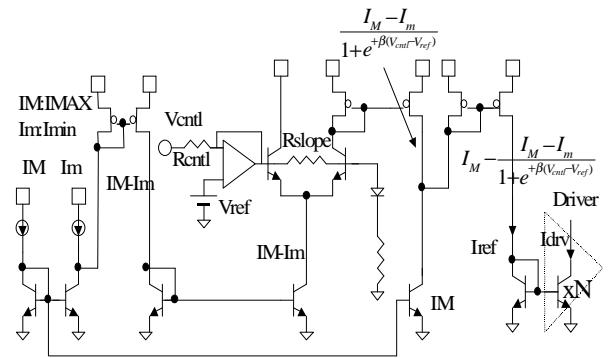

The implementation of proposed control technique is shown in Fig. 3 and is operated as the following equation:

$$I_{drv} = N \left( I_{MAX} - \frac{I_{MAX} - I_{min}}{1 + e^{\beta(V_{ctrl}-V_{ref})}} \right) \quad (2)$$

where  $I_{MAX}$ ,  $I_{min}$  represent maximum and minimum bias current, respectively and  $V_{ctrl}$ ,  $V_{ref}$  represent control and reference voltage, respectively and  $\beta$  relates to gain slope parameter and  $N$  is the area ratio of driver to reference. The gain slope at center point ( $V_{ref}$ ) can be expressed as

$$\frac{\partial I_{drv}}{\partial V_{ctrl}} \bigg|_{V_{ctrl}=V_{ref}} = \beta \frac{(I_{MAX} - I_{min})}{4} \quad (3)$$

$$\beta = \frac{R_{slope}}{R_{ctrl}} \frac{q}{kT} \quad (4)$$

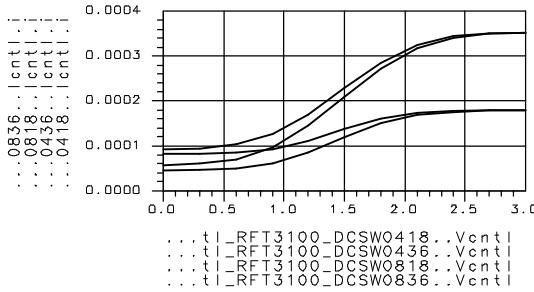

It can be controlled by the ratio of  $R_{slope}$  to  $R_{ctrl}$  and the center point can be controlled by  $V_{ref}$ . The simulated results with several bias combinations by HP ads are drawn in Fig. 4. It shows that the simulated results agree well with equation. This bias control block is under fabrication.

Fig. 3. The implemented bias control circuit to decrease bias current [5].

Fig. 4. The simulated results of bias reference current ( $I_{ref}$ ) on such combinations as:

- A.  $I_{min}=80 \mu A$ ,  $I_{max}=360 \mu A$ .

- B.  $I_{min}=80 \mu A$ ,  $I_{max}=180 \mu A$ .

- C.  $I_{min}=40 \mu A$ ,  $I_{max}=360 \mu A$ .

- D.  $I_{min}=40 \mu A$ ,  $I_{max}=180 \mu A$ .

X-axis and y-axis represents control voltage (V) and bias reference current (A), respectively. Here,  $V_{ref}=1.41$  V,  $R_{ctrl}=80 \text{ k}\Omega$ , and  $R_{slope}=5 \text{ k}\Omega$ .

### III. MEASUREMENT

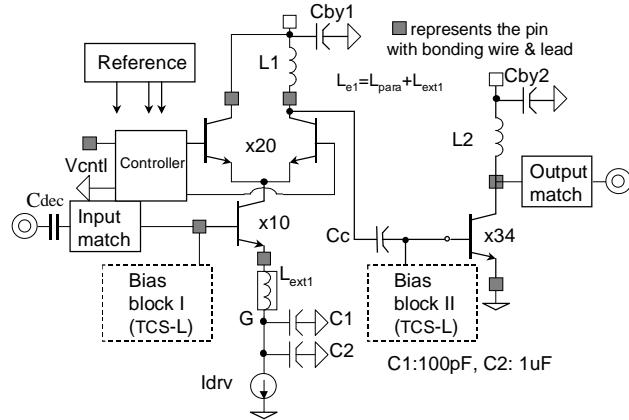

To verify the above description, the 1st stage of our previous circuit [3] is modified as shown in Fig. 5. To control bias current, an external current source is used and the node G is ac grounded by external two capacitors (1uF and 100pF). Two capacitors are used to ground at both lower and RF frequencies.

Fig. 5. The used schematic of driver amplifier to control bias current.

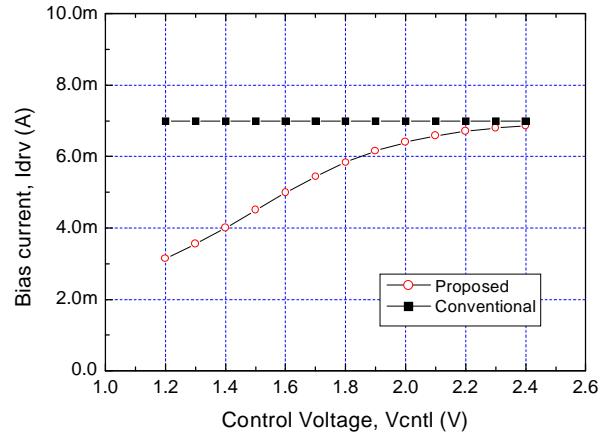

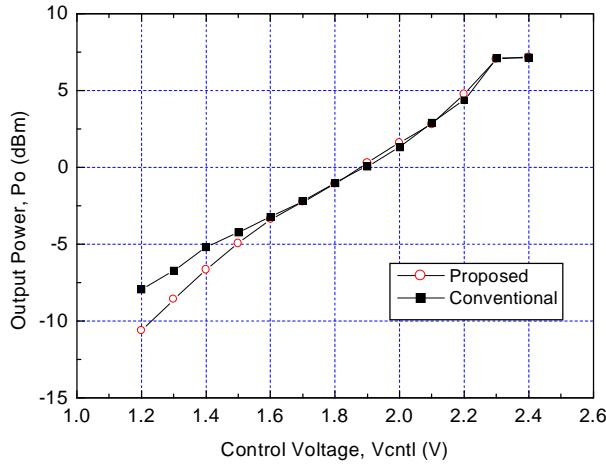

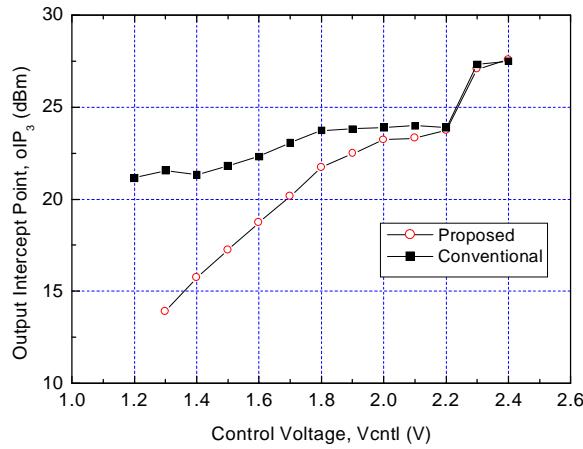

To clarify the difference between conventional method and our proposed technique, each performance is compared at the same condition except bias current of the 1st stage. Both gains are controlled by  $V_{ctrl}$ . The external current source is controlled by HP VEE program. The bias current ( $I_{drv}$ ) is controlled by (2) at proposed technique. Fig. 6(a) shows bias current with respect to

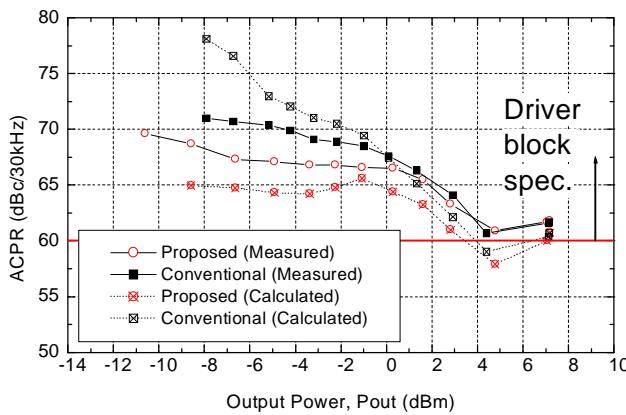

control voltage in both cases. Fig. 6(b) shows output power with respect to control voltage. This figure also represents a gain indirectly because input power is fixed to constant at  $-22$  dBm. Even though bias current is decreased by amount of 50 % at 1.3 V, Fig. 6(b) shows that measured gain is changed less than 2 dB compared to conventional one. The gain variation is not problematic but can be used to enhance gain dynamic range. Fig. 6(c) shows oIP3 with respect to control voltage. As anticipated, oIP3 is decreased as bias current is decreased at proposed technique. However, measured ACPR is not degraded than one of maximum output power due to simultaneously decreasing output power. All value of ACPR is above 60 dBc over range of output power. Still, the worst ACPR exists at maximum output power. To verify our assumption about the relation between oIP3,  $P_o$  and ACPR, calculated ACPR by (1) is drawn together with measured ACPR at Fig. 6(d). This figure shows that calculated ACPR follows the same trend well with the measured one across all power levels.

### IV. CONCLUSION

On the basis of relationship among oIP3,  $P_o$  and ACPR, it is shown that oIP3 can be decreased as output power is decreased in the condition of constant ACPR. A new bias control technique is proposed to reduce excessive bias current at lower output power. It is verified by indirect measurement that ACPR can be met at reduced current by amount of 22 % over control range. According to CDG field data [8], average transmit power is at least 15-30 dB less than maximum power, so current reduction ratio by our proposed technique becomes higher in real application. Our proposed technique can be more effective in power amplifier and LNA application.

Fig. 6(a) Bias current vs. control voltage

Fig. 6(b) Output power vs. control voltage

Input power = -22 dBm

Fig. 6(c) Output intermodulation intercept point vs. control voltage

Fig. 6(d) Adjacent Channel Power Ratio vs. output power

Fig. 6. The comparison of characteristic between conventional constant current and our proposed current control. Box, circle represents measured conventional (constant) and proposed bias control, respectively. Cross mark represents the calculation by (1) based on measured data in Fig. 6(b) and (c). Operating frequency is 850 MHz.  $V_{ref}=1.5$  V,  $\beta=4$ ,  $I_{min}=2$  mA, and  $I_{max}=7$  mA.

## REFERENCES

- [1] Jin-Su Ko, J.-K. Kim, B.-K. Ko, D.-B. Cheon, and B.-H. Park, "Enhanced ACPR Technique by Class AB in PCS Driver Amplifier," *IEEE Intern. Conf. on VLSI and CAD*, Seoul, Nov., 1999.

- [2] Q. Wu, H. Xiao, and F. Li, "Linear RF Power Amplifier design for CDMA signals: a spectrum analysis approach," *Microwave Journal*, pp.22-40, Dec., 1998.

- [3] Jin-Su Ko, H.-S. Kim, B. Kim, and B.-H. Park, "High frequency intermodulation analysis of cascode amplifier," *IEEE Asia-Pacific Conf. on ASICs*, pp.167-170, Korea, Aug., 2000.

- [4] Jin-Su Ko, J.-K. Kim, B.-K. Ko, D.-B. Cheon, S.-O. Lee and B.-H. Park, "A Class AB BiCMOS PCS Driver Amplifier with External Gain control," *IEEE Asia-Pacific Conf. on ASICs*, pp.79-82, Korea, 1999.

- [5] Jin-Su Ko, "Bias control block by min, max current to increase dynamic range on low power consumption," Patent pending, 2000.

- [6] K.-I. Jeon, "A study on the large signal behavior of GaAs FETs," *Ph.D. thesis, Ch.4. Analysis of intermodulation behavior in class AB amplifier*, KAIST, Korea, 1997.

- [7] Qualcomm, RFT3100 datasheet, 2000.

- [8] CDG (CDMA Development Group) Field Data, 1998. Courtesy of CDMA Development Group, Stage 4 system performance test.